大日本印刷(株)〔以下:DNP〕は、次世代の半導体パッケージで重要な役割を果たす、複数の半導体チップと基板を電気的に接続する中継部材で高性能な「インターポーザ」を開発した。

この部材のさらなる機能開発と2024年の量産化に向けて、DNPは、次世代半導体パッケージの評価技術・材料・基板・装置の開発を行うコンソーシアム「JOINT2」*1に参画した。

【開発の背景】

デジタルトランスフォーメーション(DX)が世界的に進展し、特に第5世代(5G)やそれ以降(ポスト5G)の次世代通信システム、人工知能(AI)等でより高性能な半導体製品が求められるなど、半導体市場のさらなる成長が期待されている。この半導体製品の高機能化・高速化・低消費電力化には、シリコンウエハ上のパターンの微細化技術が必要だが、プロセスの複雑化と高コスト化により、さらなる微細化が限界に近づいていると言われている。

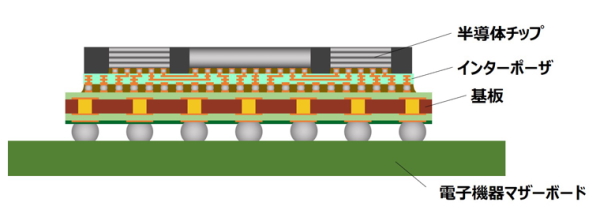

こうした課題に対し、CPU(中央演算処理装置)やメモリなど、機能の異なる複数のチップを1つの基板上に高密度で実装し、処理速度を向上させるパッケージング技術が注目されている。今回DNPは、この技術で重要な役割を果たす、複数の半導体チップと基板を電気的に接続する中継部材である「インターポーザ」を開発した。

【DNPが開発したインターポーザについて】

DNPは、「印刷」プロセスから応用・発展させたコアテクノロジー「微細加工技術」を活用して、半導体回路パターンの描画用原版「フォトマスク」や次世代のパターン転写技術であるナノインプリントリソグラフィー用の「テンプレート」の製造、センサ等のMEMS(微小電子機械システム)のファンドリーサービスなどを広く展開している。

今回、これらの事業を通じて培った、ガラスやシリコンの基板の加工およびハンドリング技術、微細配線形成技術等を応用して、高性能な「インターポーザ」を開発した。配線の微細化によって顕在化する“配線層の劣化に伴う配線抵抗の上昇や配線間絶縁性の低下”といった課題を解決し、次世代の半導体パッケージに必要な高性能かつ微細な配線を実現するという。

【今後の展開】

DNPは、JOINT2における開発と参画企業との協業により、「インターポーザ」の機能開発と量産化の取り組みを加速し、次世代半導体のパッケージング技術の開発を推進する。また、独自の「P&I(印刷と情報)」の強みを活かし、次世代通信向け電子部品とIoT(モノのインターネット)の情報セキュリティを高めるプラットフォームを提供するなど、快適な情報社会を支えるソリューションを提供していくとしている。

*1 JOINT2(Jisso Open Innovation Network of Tops 2:ジョイント2)

次世代半導体の実装技術や評価技術を確立することを目的とし、半導体実装材料・装置の開発に携わる企業12社が参画するコンソーシアム。昭和電工マテリアルズ(株)が幹事会社となり、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の公募事業「ポスト5G情報通信システム基盤強化研究開発事業/先端半導体製造技術の開発」に採択された。

ニュースリリースサイト(DNP):https://www.dnp.co.jp/news/detail/10161685_1587.html