量子集積エレクトロニクス研究センター

教授 池辺 将之

3.ピクセル並列ADCアーキテクチャによるグローバルシャッタ型テラヘルツイメージャ20)

3.1 提案型CMOSテラヘルツイメージャの概要

現在は、シリコンCMOSによる検波回路の進歩により、アレイ化した後の読み出し要素も含めたシステム統合の研究開発へシフトする動きも見られている。アンテナ型回路は、アンテナがピクセル部の大半を占め、余剰な回路を組み込みやすい。そこで、ピクセル部にアナログ積分器を集積する12)、ピクセル並列のA/D変換器のブロック配置を工夫する13)などのセンサシステム全体の考慮が必要となる。この場合でも、どのA/D変換器(Single Slope型、SAR型、ΔΣ型、VCO型など)を採用するかも考える必要がある。同時に、ピクセル部の製造バラツキを、オフセット/利得の面でいかに補償するかが、重要となる。各ピクセルに補償用のメモリを持つなどの解決手段も考えられる。そこで、回路負担および、補償を行うにあたりスキャンライン駆動によって1画素ごとに補償が必要になるかなど、実動作における駆動シーケンスとフレームレートへの影響、並びにセンサアレイの温度による変動と再補償の期間設定など、考慮すべき点も多い。

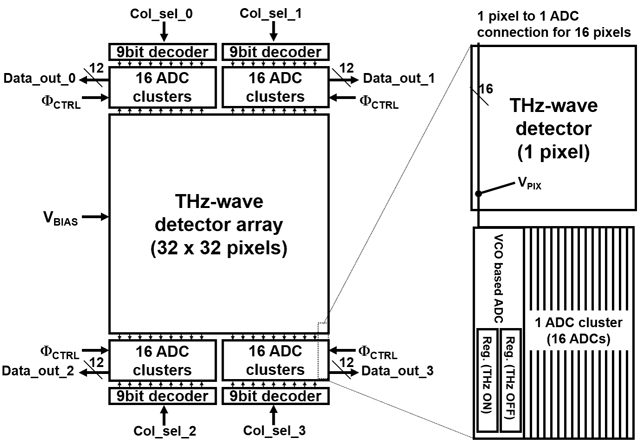

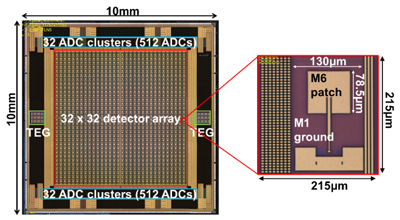

イメージャの開発に当たり、筆者らはパッチアンテナ型ピクセルを用いてアレイ構成とした。図2に設計したテラヘルツイメージャのブロック図を示す。イメージャは、32×32のテラヘルツイメージングピクセル、読み出しのためのデコーダを備えた16ADC×16クラスタ×4ブロック=1024ADC、および、4つの12-bit出力から構成される。32×32イメージャは内部で4つの16×16のサブイメージャに分割されており、これらは独立に動作する。16個のADCを含むADCクラスタは13μmの幅を持ち、これが215μmの間隔で16つ並び、16×16イメージングピクセルの下部(あるいは上部)の計4か所に配置されている。ADCはイメージングピクセルと1対1で対応しており、グローバルシャッタ動作を可能にする。さらに、各ADCにはON/OFFキーイング(OOK)変調テラヘルツイメージング用の2つのデータバッファを備え、9-bitの選択信号によって256ADCの512データバッファよりデータを選択し読み出すことが可能である。イメージャを4つのサブイメージャに分割したことにより、読み出しチャネルも4並列となるが、これはデータ読み出しの速度条件を緩和している。例えば、読み出し用デコーダを512kHzで動作させる場合、1kfpsのフレームレート(ON/OFF状態を分けると2kfps)でテラヘルツイメージを取得することが可能である。また、本テラヘルツイメージャはピクセル並列アーキテクチャを採用しているため、マルチフレーム超解像やマルチモーダルイメージングなどへの応用も可能である。

3.2 ピクセル回路の設計

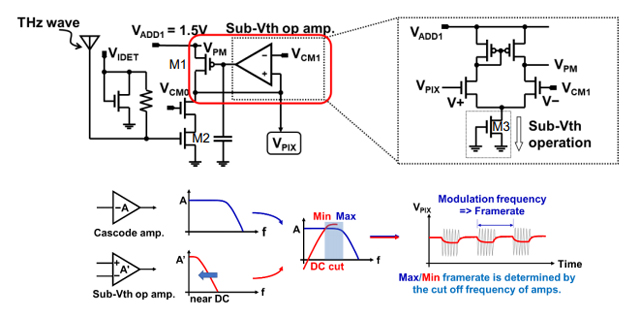

テラヘルツ光イメージング用ピクセル回路13)を図2-3 に示す。ピクセル回路はオンチップマイクロストリップアンテナ、マッチング回路、テラヘルツ検出器から構成される。また、テラヘルツ検出器は、カスコードアンプとサブスレッショルドオペアンプの2つの増幅回路から成る。カスコード増幅回路では、テラヘルツ波入力に接続されたn-MOSFET(M2)が駆動される。まず、OOK変調されたテラヘルツ信号は、カスコードアンプの入力段であるn-MOSの2章で述べた特性により包絡線検波回路として動作すると共に検出信号を増幅する。p-MOSFET(M1)は負荷抵抗として扱う。サブスレッショルド増幅回路を接続し、フィードバック回路として用いることで、M1 の負荷抵抗の値を決定する。この回路は、Tail電流源であるM3のゲートを接地することで1nA程度の微弱な電流を流す増幅回路として働く。サブスレッショルド増幅回路は大きな時定数を持つため、直流から極低周波(カットオフ周波数数10Hz)で動作する。フィードバックループを含めた検出器全体として見ると、サブスレッショルド増幅回路の動作領域が遮断されるため、検出器のDC オフセットを取り除くことができる。

マイクロストリップアンテナは、180 nm CMOS プロセスにおいて、メタル1層とメタル6層により形成する。アンテナもSi 基板上に同時集積することで、検出器とのワンチップ化が可能である。アンテナの形状は0.9 THz 近傍で動作するように電磁界シミュレータを用いて設計した。アンテナサイズは130×78.5 μm2 である(図4)。

3.3 Voltage-Controlled Oscillator Based ADC

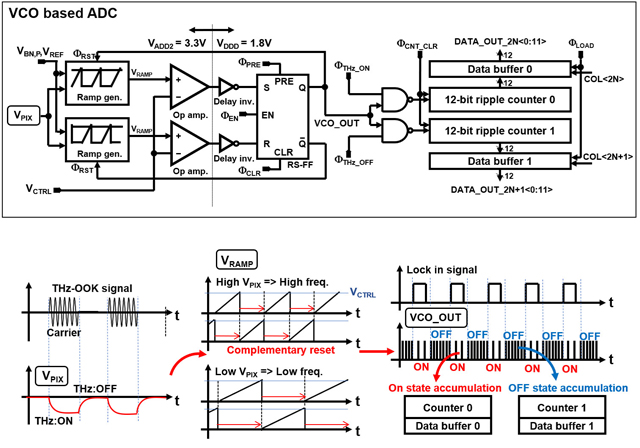

図5にVCO-Based ADCのブロック図を示す。ADCは2つのランプ信号発生器、オペアンプ、SR-FF、および、2つの12-bitカウンタによって構成される。一方のランプ信号発生器の出力が閾値電圧VCtrlを超えると、もう一方のランプ信号発生器に対しリセット信号が入力される。このように、2つのランプ信号発生器が相補的にリセットを行うことで、デューティー比50%のクロック信号を生成することが可能になる。また、ランプ信号の傾き(クロック周波数の決定に関わる)は、イメージングピクセルから入力される電圧によって決定される。このクロック信号をカウンタへ入力することで、ピクセルから出力されるアナログ電圧値をディジタル値に変換する。また、カウンタはOOK変調信号を扱うためにVCO-Based ADCごとに2つずつ用意され、テラヘルツ波がON/OFFそれぞれの状態について変換値を保持することができる。また、カウンタの変換(カウントアップ)動作の際に、保持された前時刻の変換値を読み出すことも可能である。

4.撮像実験と結果

本テラヘルツイメージャの撮像実験のための光源として、周波数可変テラヘルツ波源である光注入型テラヘルツパラメトリック発生器(is-TPG: injection-seeded THz-wave Parametric Generator)を利用した14)。is-TPGはYAGレーザーによるSeed/Pump光を非線形光学結晶であるMgO:LiNbO3により周波数混合し、差分THz光をSi プリズムにより取り出す(協力:理化学研究所)。

Responsivity は検出された出力電圧をアンテナに入射された電力で割ることで求めた。テラヘルツ光源の出力とビームプロファイルから求められたアンテナ面積(78。5μm×78.5μm)あたりの応答性は218kV/W@0.93THzであり、ピクセル面積(215μm×215μm)あたりの応答性は34.6kV/W@0.93THzであった。また、測定されたNEPは91 pW/Hz1/2@31Hzであり、テラヘルツ波パルスを100kHzでOOK変調した場合の推定NEPは13.7 pW/Hz1/2@100kHzである。

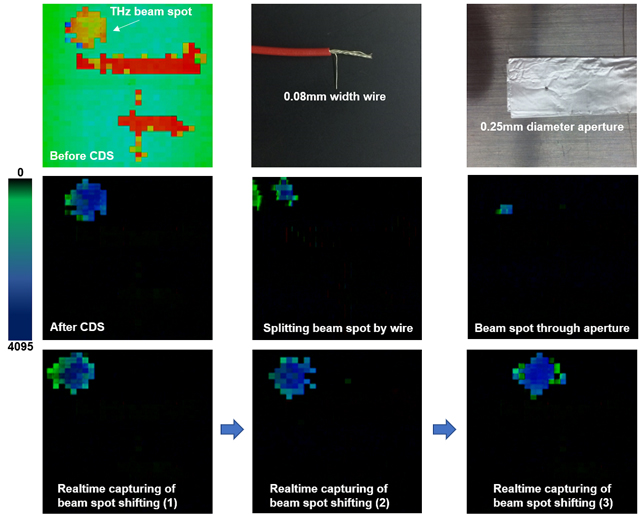

図6に撮像結果を示す。ただし、使用したテラヘルツ波光源のOOK変調周波数は200Hzであり、これにより本実験におけるテラヘルツイメージャのフレームレートは 400fpsに制限されている。テラヘルツ波ビームの形状はガウシアンであり、平均パワーは18.8μw@0.93THzである。図8左上はTHzONでの撮像結果であり、図中左上にテラヘルツ波ビームスポットと、図中中央付近に顕著な固定パターンノイズを見ることができる。撮像結果に対して外部CDSを行うことで、固定パターンノイズを取り除くことが可能であり、図6の左上以外の6つの撮像結果はすべて外部CDS後の像である。図8左側中段は図8左上の撮像結果に対して外部CDSを行ったものであり、固定パターンノイズを除いたビームスポットの形状を確認できる。ビームスポットに対し、直径0.08mmの金属細線をかざして撮像した結果が図8中央である。テラヘルツ波ビームスポットが金属細線によって2つに分断されている様子が確認できる。また、ビームスポットに対し、直径0.25mmの開口部を持つ金属箔をかざして撮像した結果が右側中段である。テラヘルツ波ビームスポットが開口部によって絞られ、より小さなスポットとして撮像されている様子が確認できる。図8最下段の3つの像はビームスポットの移動を観察している様子である。ビームスポットが左から右に向けて移動していくことがリアルタイムで観察された(ON/OFF Keying:400fps, CDS後200fps)。

参考文献

12) Al Hadi, Richard, et al. “A 1 k-pixel video camera for 0.7?1.1 terahertz imaging applications in 65-nm CMOS.” IEEE Journal of Solid-State Circuits 47.12 (2012): 2999-3012.

13) Y. Sayuri, et al. 5.8 A 32× 32-Pixel 0.9 THz Imager with Pixel-Parallel 12b VCO-Based ADC in 0.18 μm CMOS. In: 2019 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2019. p. 108-110.

14) S. Hayashi, et al., “Ultrabright Continuously Tunable Terahertz-Wave Generation at Room Temperature,” Scientific Reports, vol. 4, article #5045, June 2014.

【著者紹介】

池辺 将之(いけべ まさゆき)

北海道大学 量子集積エレクトロニクス研究センター 教授

■略歴

1998年 4月 日本学術振興会 特別研究員 「知的イメージセンサの研究」に従事

2000年 3月 北海道大学 大学院工学研究科 博士後期課程修了 (電子情報工学専攻)(博士(工学))

2000年 4月 大日本印刷㈱ 半導体製品研究所 勤務

2002年 8月 豊橋技術科学大学 知識情報工学専攻 受託研究員

2003年 4月 大日本印刷㈱にて 電子デバイス研究所 勤務 「無線・画像処理システムの研究・開発」に従事

2005年 4月 北海道大学 大学院情報科学研究科 准教授 「画像処理アルゴリズム/システム/センサLSIの研究・無線システム開発」に従事

2018年 4月 北海道大学 量子集積エレクトロニクス研究センター 教授 「イメージセンサ・高速画像処理(AIアルゴリズム・ソフト/ハードウェア)の研究」に従事